I’m a Graduate Research Assistant at MIT advised by Profs. Vivienne Sze and Joel Emer in the EEMS group.

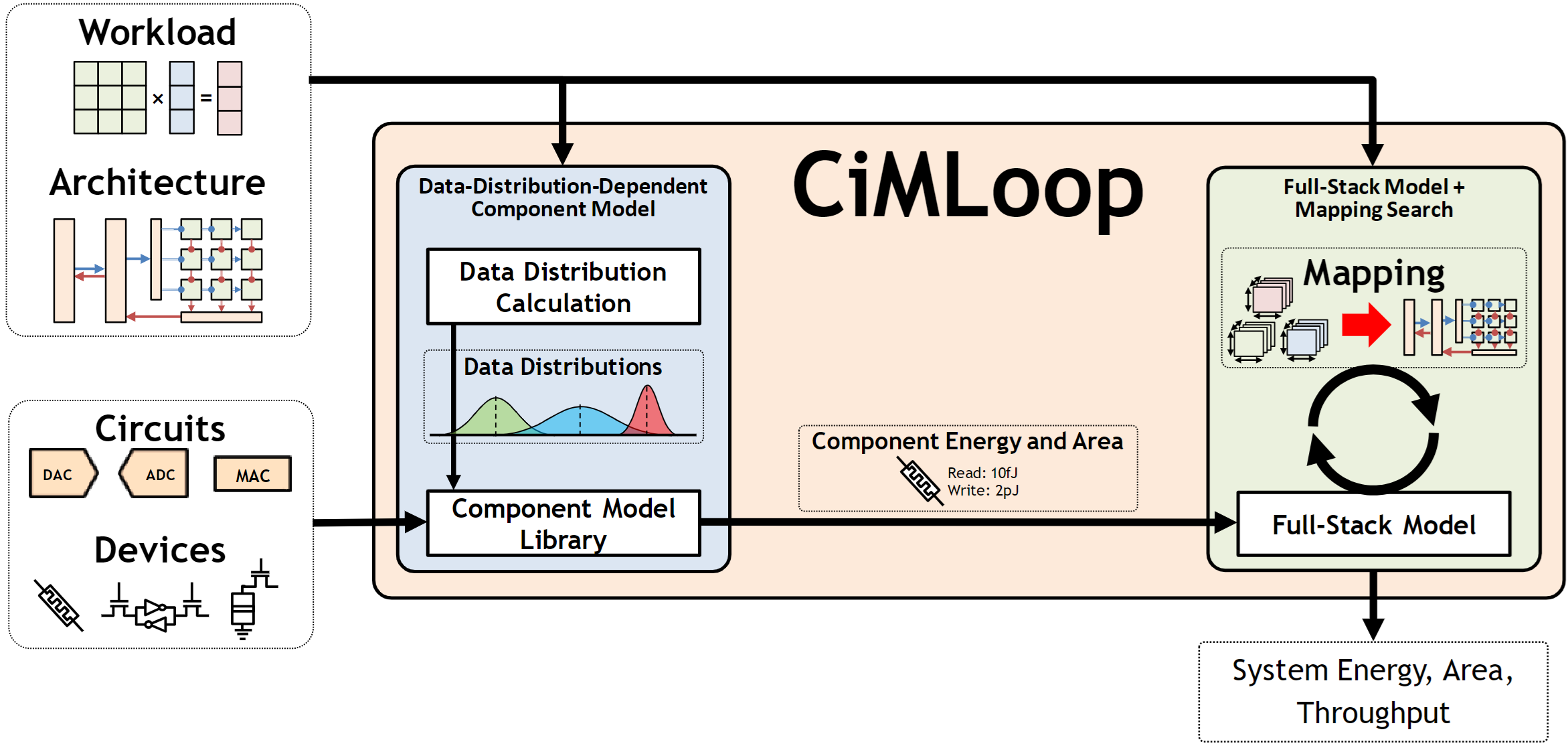

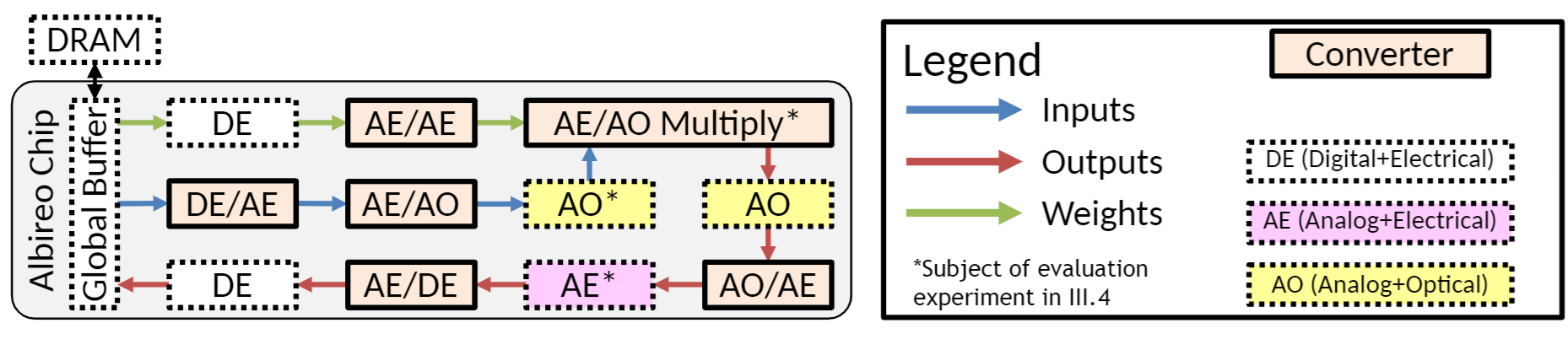

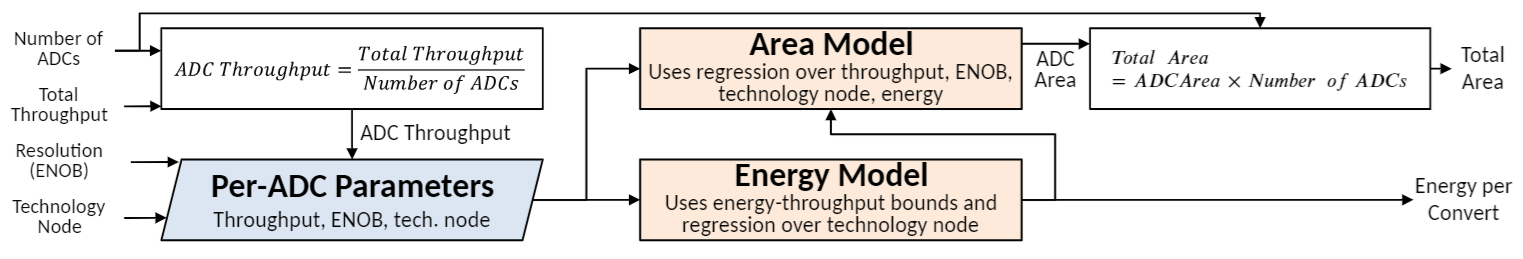

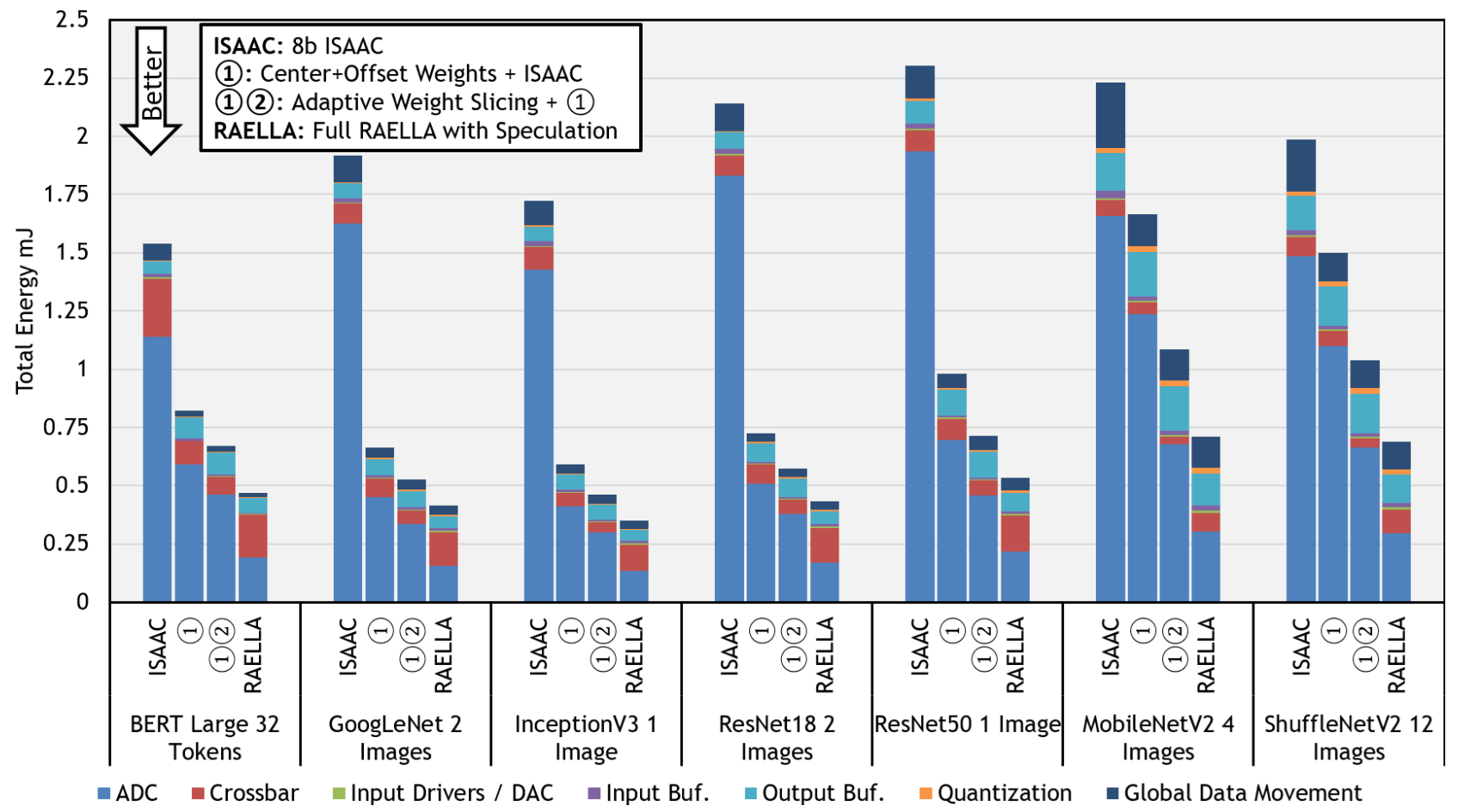

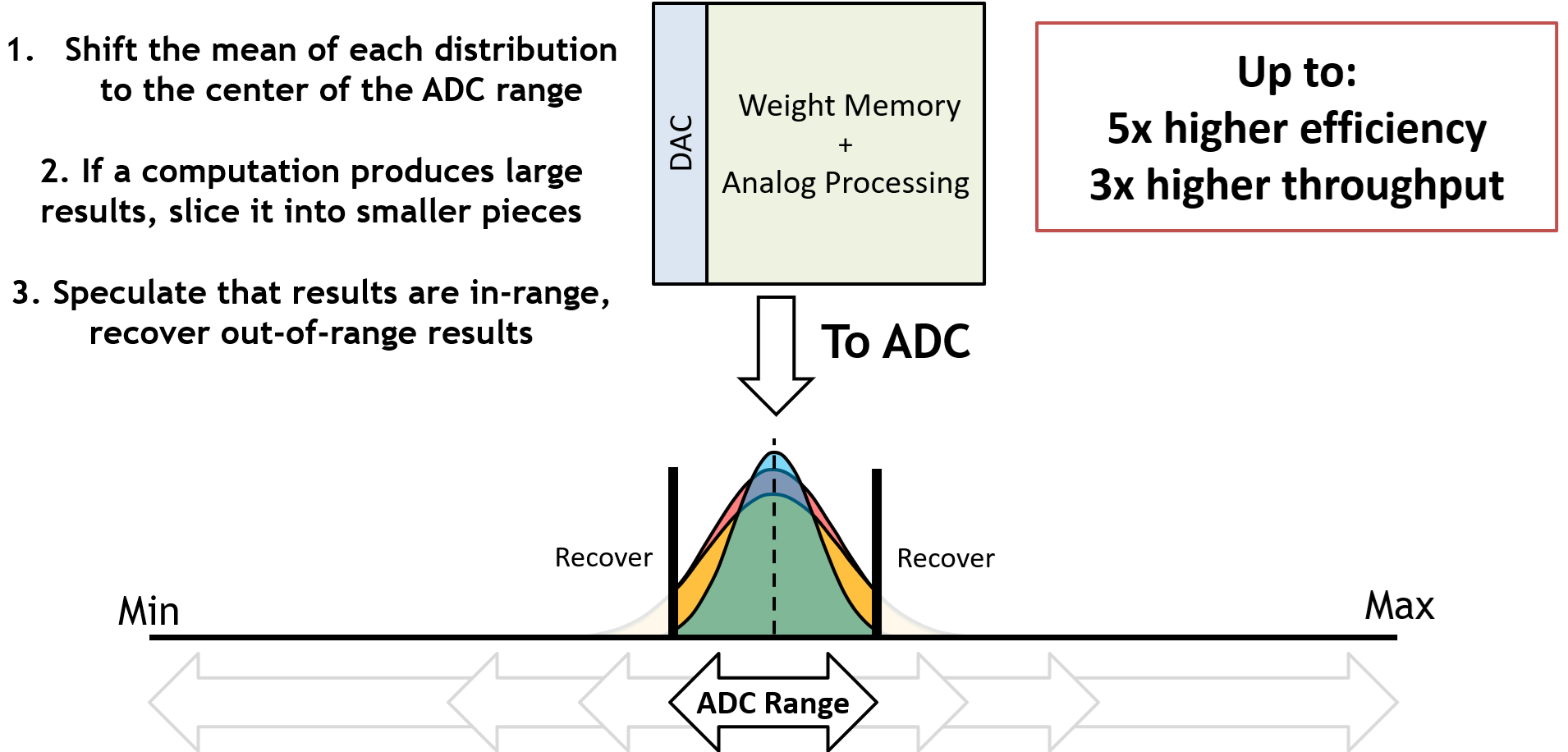

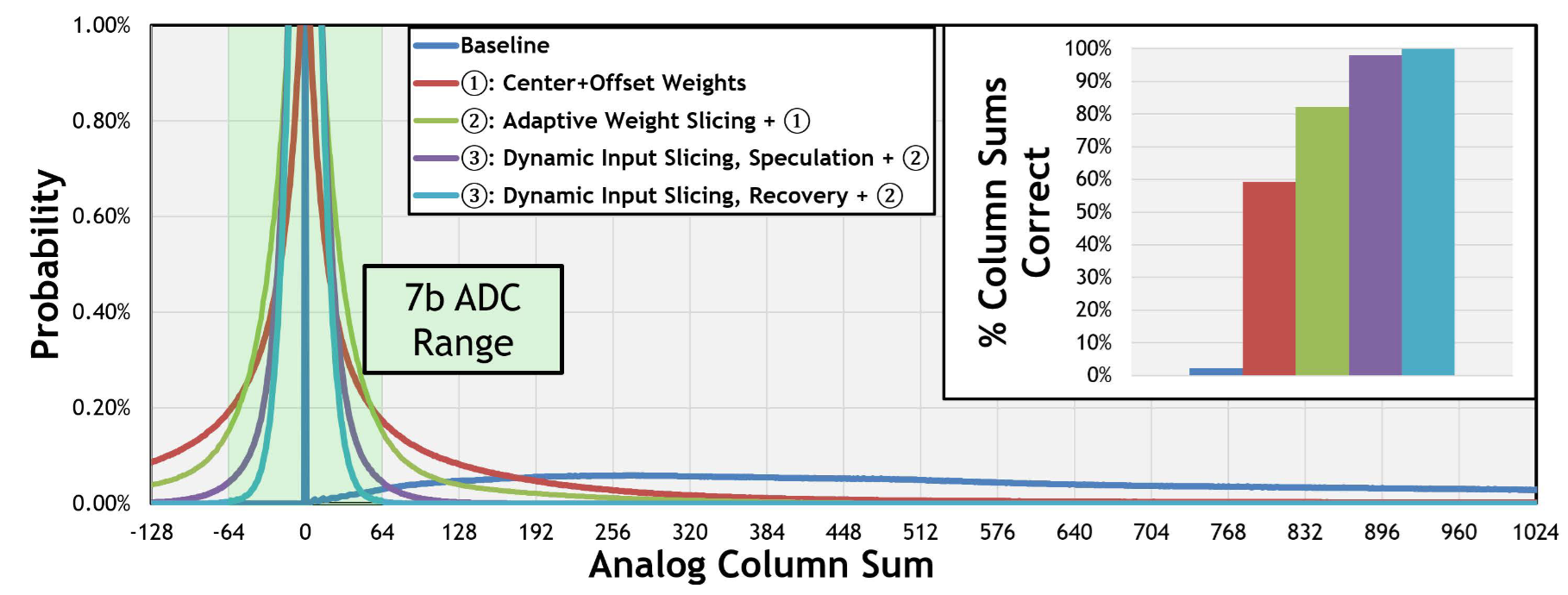

My research focuses on modeling and design of analog, compute-in-memory, and photonic deep neural network accelerators. Through cross-stack co-design, I work to develop lower-energy, higher-throughput systems.

\(~\) \(~\)

Publications and Talks

No matching items